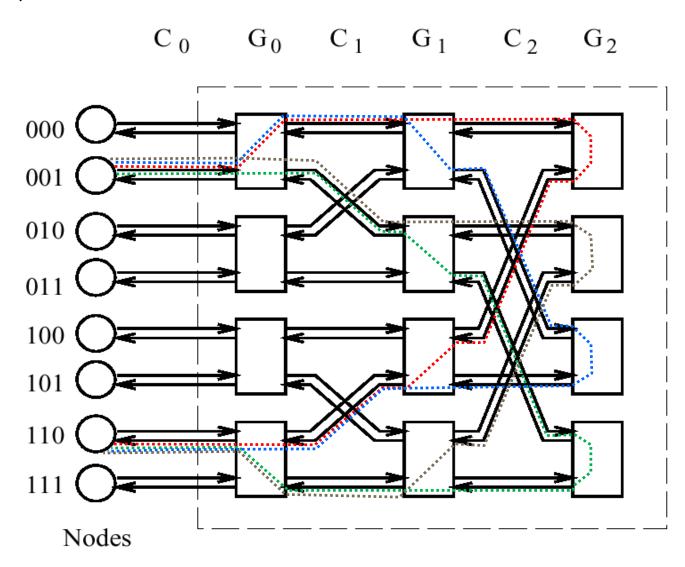

#### Problema 1 Red Omega 8x8 C0 G0 G1 G2 C1 C2 **C**3 D0 **S**0 D1 **S1** D2 **S2 3B** B D3 **S**3 **S**4 D4 **S**5 D5 D6 **S6** D D7 **S7**

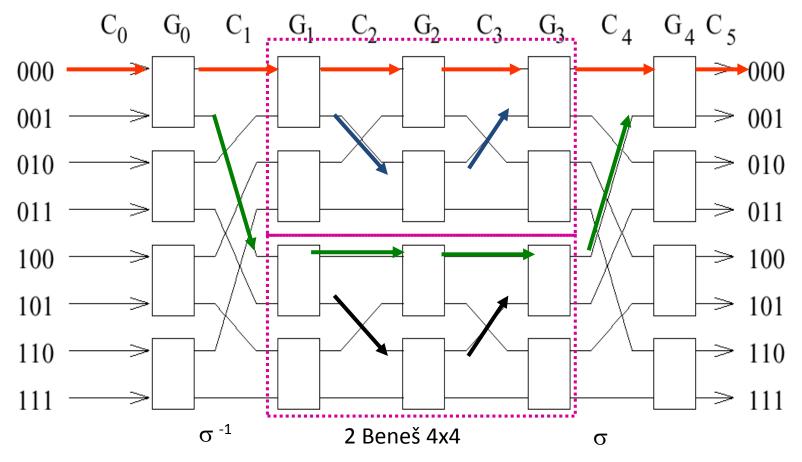

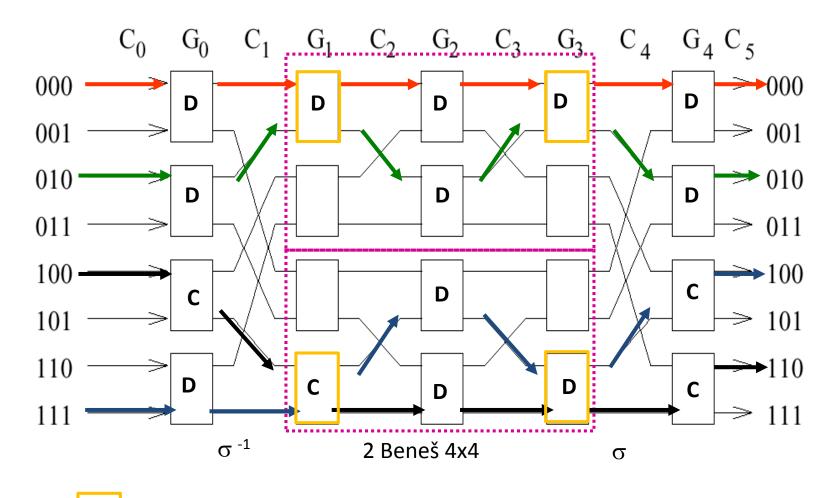

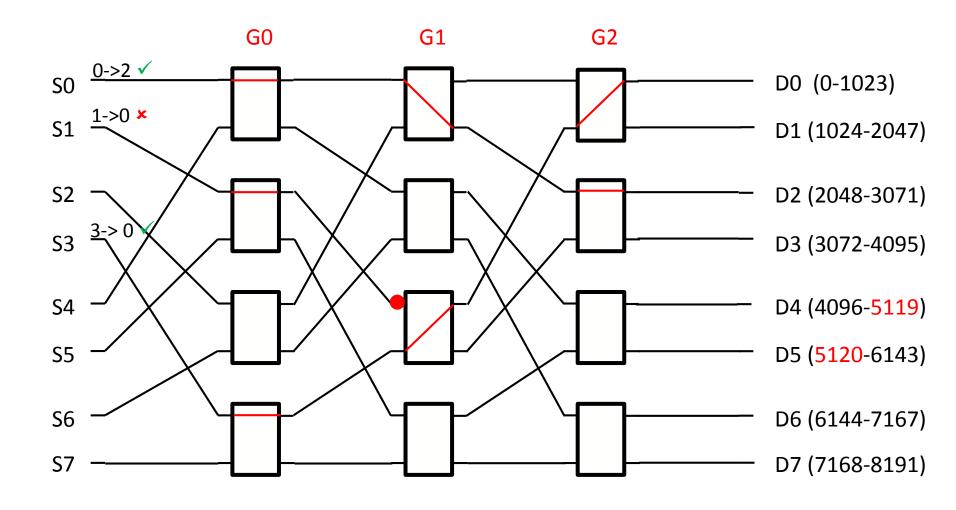

Observando la figura vemos que como consecuencia de la conexión cortada:

- D2 queda desconectado de: S0, S4, S2 y S6

- D3 queda desconectado de las mismas fuentes

En etapa G0 hay dos caminos: directo (D) y cruzado (C). En etapa G1, para cada uno de los anteriores, hay dos caminos: directo y cruzado.

Con esto ya llegamos a G2 (etapa central). A partir de ahí, los caminos divergentes tienen que converger hacia D0. Por tanto los caminos se muestran e la tabla de al lado

|       | G0 | <b>G1</b> | G2 | G3 | G4 |

|-------|----|-----------|----|----|----|

| Cam 1 | D  | D         | D  | D  | D  |

| Cam 2 | D  | С         | D  | С  | D  |

| Cam 3 | С  | D         | D  | D  | С  |

| Cam 4 | С  | С         | D  | С  | С  |

Nodos con las dos entradas en uso

C: Conexión cruzada D: Conexión directa

### a) Red Omega 4096x4096.

### Calculamos el nº de etapas:

$N = K^n$ , donde N=puertos, k = base (grado del conmutador) = 2, n = etapas  $n = log_2 4096 = 12$  etapas

tc = 2 ns; tr (retardo conmutador) = 0,2 ns

<u>Delay slots de un Load:</u> viene dado por el viaje de ida y vuelta:

Procesador → Mem (envío de la dir) + Mem → Procesador (recepción del dato)

t acceso a Mem =  $2 \times (retardo conmutador) \times (n^o etapas) = 2 \times (0.2 \times 12) = 4.8 \text{ ns.}$

Como 1 ciclo = 2 ns, esto implica que el delay slot debe ser un entero de ciclos mayor o igual que 4,8/2. Es decir: delay slot = 3 ciclos

### b) Red Benes

Etapas = 2x12 - 1 = 23

t acceso a Mem =  $2 \times (0.2 \times 23) = 9.2 \text{ ns.} \rightarrow \text{delay slot} = 5 \text{ ciclos}$

Red Omega de 1024 nodos con conmutadores 4x4.

### En general:

$N = K^n$ , donde N=puertos, k = base (grado del conmutador), n = n0 de etapas N0 de conmutadores = (N/k) x n

### En este problema:

- a)  $N = 1024 = 2^{10}$ ,  $k = 4 \rightarrow N = 4^n$ , Igualando  $2^{10} = 4^n$ ;  $(2^2)^5 = (2^2)^n => n = 5$  etapas

- b)  $N^{\circ}$  de conmutadores =  $(2^{10} / 4) \times 5 = 256 \times 5 = 1280$  conmutadores

### Red Omega con 16 entradas, conmutadores 2x2. Conectar $11 \rightarrow 5$ y $7 \rightarrow 9$

- Dir destino: (d3,d2,d1,d0)

- di selecciona el funcionamiento de los conmutadores de la etapa n-i-1

- di = 0 → Salida superior

- di = 1 → Salida inferior

Caminos Compatibles!

Red Omega de 512 nodos con conmutadores 8x8.

### En general:

$N = K^n$ , donde N=puertos, k = base (grado del conmutador), n = n0 de etapas N0 de conmutadores = (N/k) x n

### En este problema:

- a)  $N = 512 = 2^9$ ,  $k = 8 \rightarrow N = 8^n$ , Igualando  $2^9 = 8^n$ ;  $2^9 = (2^3)^n => n = 3$  etapas

- b)  $N^{\circ}$  de conmutadores =  $(2^{\circ} / 8) \times 3 = 64 \times 3 = 192$  conmutadores

- c) N =  $4096 = 2^{12}$  nodos  $2^{12} = (2^3)^n \implies n = 4$  etapas Nº de conmutadores =  $(2^{12} / 8)$  x  $4 = 2^{11} = 2048$  conmutadores Conmutadores adicionales = 2048 - 192 = 1856 conmutadores

a) 4 <del>></del> 7

b) 1 → 6

| Ciclo     | P0                     | P1           | P2           | Р3        | P4           | P5           | P6           | P7          |

|-----------|------------------------|--------------|--------------|-----------|--------------|--------------|--------------|-------------|

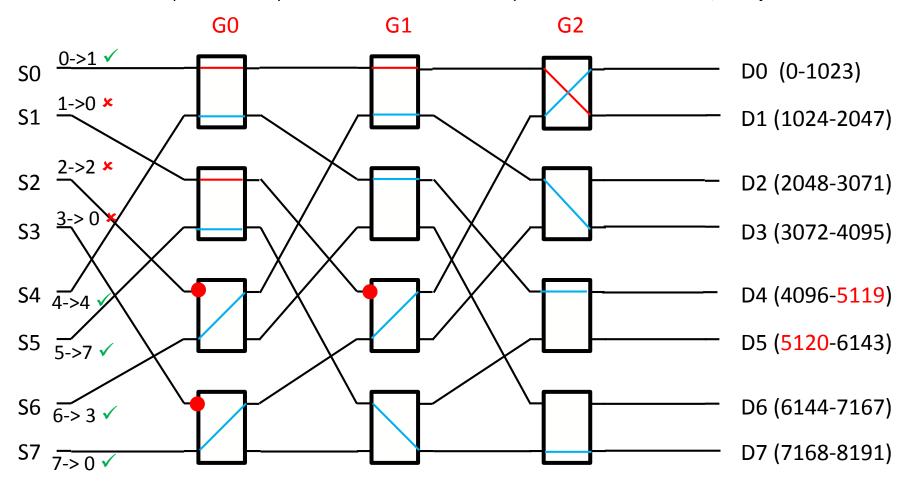

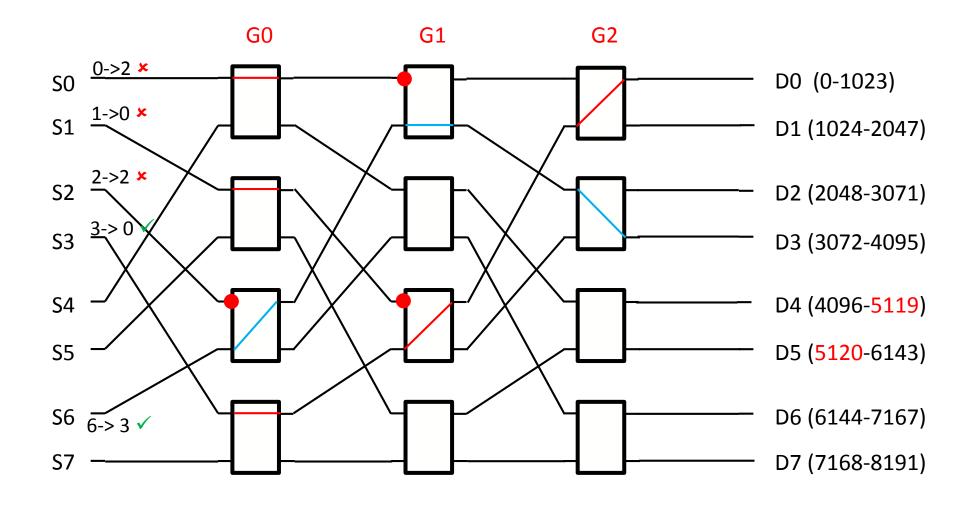

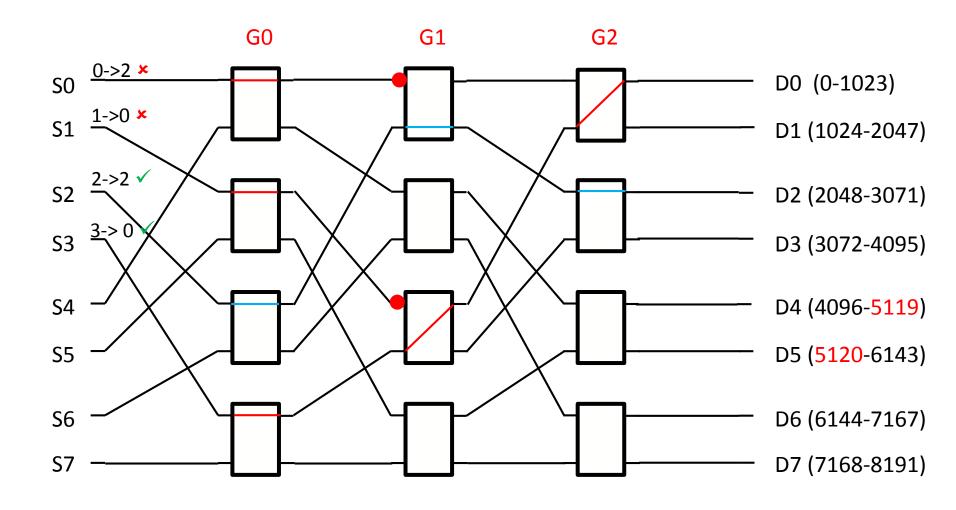

| Intento 1 | Dir: 1025<br>Con: 0->1 | 100<br>1->0  | 3000<br>2->2 | 0<br>3->0 | 5020<br>4->4 | 7800<br>5->7 | 4000<br>6->3 | 670<br>7->0 |

| Exitos 1  | $\checkmark$           | ×            | ×            | ×         | ✓            | $\checkmark$ | $\checkmark$ | ✓           |

| Intento 2 | Dir: 2048<br>Con: 0->2 | 100<br>1->0  | 3000<br>2->2 | 0<br>3->0 |              |              | 4001<br>6->3 |             |

| Exitos 2  | ×                      | ×            | ×            | ✓         |              |              | ✓            |             |

| Intento 3 | Dir: 2048<br>Con: 0->2 | 100<br>1->0  | 3000<br>2->2 | 1<br>3->0 |              |              |              |             |

| Exitos 3  | ×                      | ×            | ✓            | ✓         |              |              |              |             |

| Intento 4 | Dir: 2048<br>Con: 0->2 | 100<br>1->0  |              | 2<br>3->0 |              |              |              |             |

| Exitos 4  | ✓                      | ×            |              | ✓         |              |              |              |             |

| Intento 5 | Dir: 8000<br>Con: 0->7 | 100<br>1->0  |              |           |              |              |              |             |

| Exitos 5  | ✓                      | ✓            |              |           |              |              |              |             |

| Intento 6 |                        | 2500<br>1->2 |              |           |              |              |              |             |

| Exitos 6  |                        | ✓            |              |           |              |              |              |             |

| Intento 7 |                        | 7500<br>1->7 |              |           |              |              |              |             |

| Exitos 7  |                        | ✓            |              |           |              |              |              |             |

### Ciclo de acceso 1

Trazamos primero los caminos que tienen prioridad (entrada 1 de cada conmutador) en color azul. A continuación los que no tienen prioridad hasta donde son compatibles con los anteriores, en rojo

a)

$$T_{RC} = 0.5 \text{ ns}$$

$T_{mem} = 2 \text{ ns}$   $T_{com} = N^{\circ} \text{ de etapas x } T_{RC} = 3 \text{ x } 0.5 = 1.5 \text{ ns}$

Tciclo =

$$2 \times T_{com} + T_{mem} = 2 \times 1.5 + 2 = 5 \text{ ns}$$

Tiempo total para cada procesador = (nº ciclos Pi) x Tciclo

P0:

$$T_{total} = 5 \times 5 = 25 \text{ ns}$$

P1:

$$T_{total} = 7 \times 5 = 35 \text{ ns}$$

P2:

$$T_{total} = 3 \times 5 = 15 \text{ ns}$$

.....

....

Caso más lento P1: 35 ns

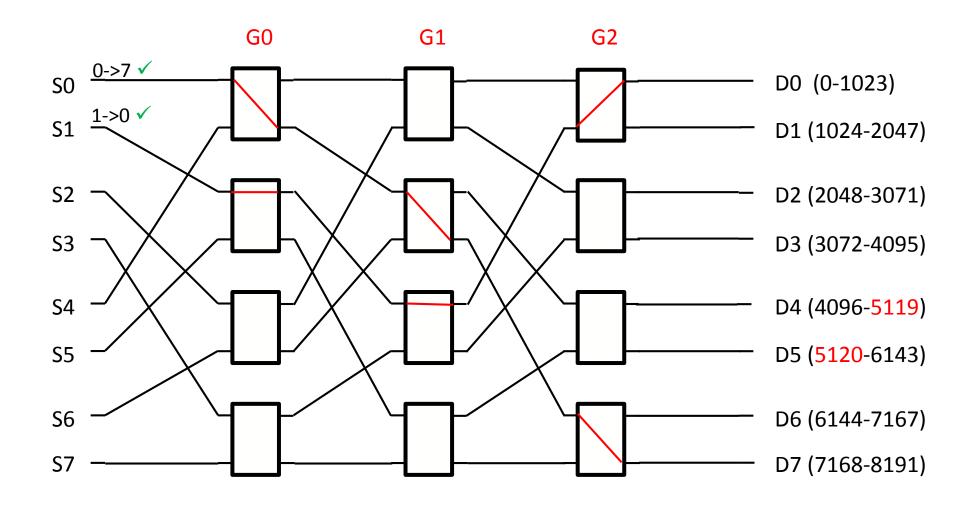

Problema 10 (Con Crossbar. En accesos a mismo destino se anulan las operaciones procedentes de puertos inferiores)

| Ciclo     | P0                                    | P1           | P2           | Р3        | P4           | P5           | P6           | P7          |

|-----------|---------------------------------------|--------------|--------------|-----------|--------------|--------------|--------------|-------------|

| Intento 1 | Direc: 1025<br>Conex: 0->1            | 100<br>1->0  | 3000<br>2->2 | 0<br>3->0 | 5020<br>4->4 | 7800<br>5->7 | 4000<br>6->3 | 670<br>7->0 |

| Exitos 1  | $\checkmark$                          | ×            | $\checkmark$ | ×         | ✓            | ✓            | ✓            | ✓           |

| Intento 2 | <b>Direc:</b> 2048 <b>Conex:</b> 0->2 | 100<br>1->0  |              | 0<br>3->0 |              |              | 4001<br>6->3 |             |

| Exitos 2  | ✓                                     | ×            |              | ✓         |              |              | ✓            |             |

| Intento 3 | <b>Dir:</b> 8000 <b>Con:</b> 0->7     | 100<br>1->0  |              | 1<br>3->0 |              |              |              |             |

| Exitos 3  | ✓                                     | ×            |              | ✓         |              |              |              |             |

| Intento 4 |                                       | 100<br>1->0  |              | 2<br>3->0 |              |              |              |             |

| Exitos 4  |                                       | ×            |              | ✓         |              |              |              |             |

| Intento 5 |                                       | 100<br>1->0  |              |           |              |              |              |             |

| Exitos 5  |                                       | ✓            |              |           |              |              |              |             |

| Intento 6 |                                       | 2500<br>1->2 |              |           |              |              |              |             |

| Exitos 6  |                                       | ✓            |              |           |              |              |              |             |

| Intento 7 |                                       | 7500<br>1->7 |              |           |              |              |              |             |

| Exitos 7  |                                       | $\checkmark$ |              |           |              |              |              |             |

b) Con un Crossbar.

Tciclo =

$$2 \times T_{com} + T_{mem} = 2 \times (4 \times 0.5) + 2 = 6 \text{ ns}$$

El Xbar tiene conectividad total, pero en un ciclo no puede haber varios procesadores accediendo a un mismo módulo de memoria. La transparencia anterior muestra el secuenciamiento de accesos, suponiendo que en caso de conflicto, la política de prioridades anula, igual que en el apartado a), las peticiones procedentes de las entradas con los números inferiores.

Por ejemplo, en el ciclo 1, P1, P3 y P7 intentan acceder al Módulo 0, pero solo P7 lo consigue.

Como muestra la tabla, con esta política de prioridades, hacen falta 7 ciclos. Con otras políticas el nº de ciclos puede variar (ver transp. siguiente). Luego:

$$T_{total} = 7 \times 6 = 42 \text{ ns}$$

Speedup = 35/42 = 0,83

Es decir, la velocidad no mejora, sino que empeora.

c) Posterga durante mucho tiempo los accesos de algunos procesadores. Vía de solución: alternar la política de prioridades.

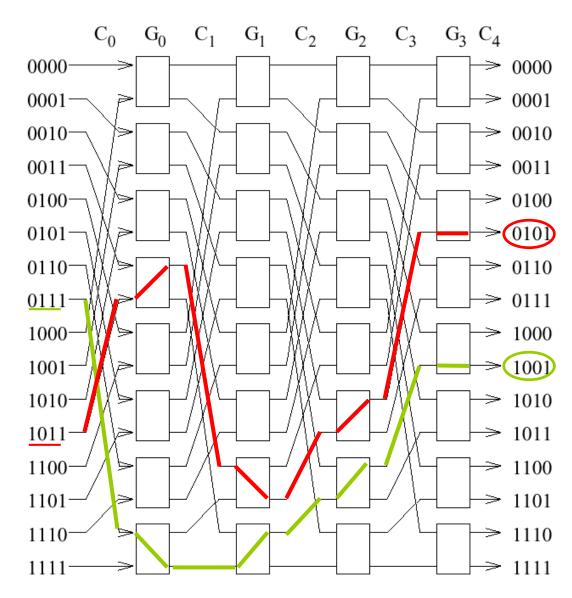

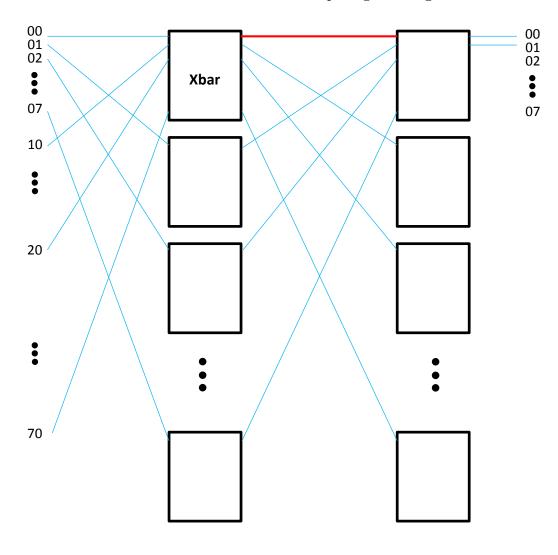

<u>Problema 12</u> Línea roja. Las conexiones internas \* y \*\* quedan ocupadas al conectar 0→0

Línea verde. Conexiones bloqueadas por el uso de \*: S4 con D4, D5, D6 y D7 Línea morada. Conexiones bloqueadas por el uso de \*\*: S1, S5, S9 y S13 con D1

#### Red Omega de 16 entradas

Tamaño mensaje: n=128 bits; Ancho de banda:  $B=1GB/s=8x10^9$  bits/s

Retardo conmutador grado 2:  $\Delta_2$  = 4x10<sup>-9</sup> s; Retardo conmutador grado 4:  $\Delta_4$  = 6x10<sup>-9</sup> s

#### Con conmutadores de grado 2 => Nº etapas (hops): h=4

Con cut-through:  $T_{CT2} = h \Delta_2 + n/B = 4x4x10^{-9} s + (128 bits / 8x10^9 bits/s) = 32x10^{-9} s = 32 ns$

Con store-and-forward:  $T_{SF2} = h (\Delta_2 + n/B) = 4 \times [4 \times 10^{-9} + (128 / 8 \times 10^{9})] = 80 \text{ ns}$

#### Con conmutadores de grado 4 => Nº etapas: h=2

Con cut-through:  $T_{CT4} = h \Delta_4 + n/B = 2x6x10^{-9} + (128 / 8x10^9) = 28 \text{ ns}$

Con store-and-forward:  $T_{SF4} = h (\Delta_4 + n/B) = 2 \times [6 \times 10^{-9} + (128 / 8 \times 10^9)] = 44 \text{ ns}$

#### Análisis:

- La opción más rápida es CT4.

- Se observa que con CT el nº de etapas de la red no influye excesivamente.

- Sin embargo, con SF el nº de etapas es muy determinante.

N= 64; Base k =8; N =  $k^n \rightarrow N^o$  etapas = n = 2

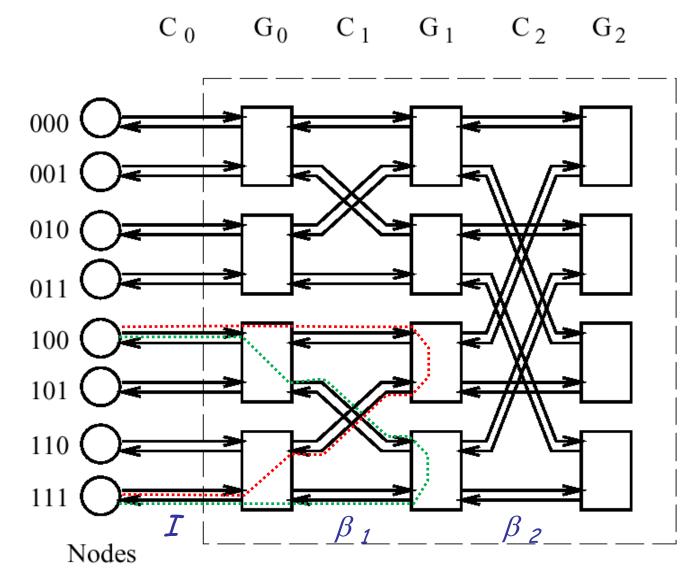

Red Omega:  $C_0 = C_1 = \sigma$ ;  $C_2 = I$ ;  $\sigma(a,b) = (b,a)$  siendo  $a,b \in \{0..7\}$

Al conectar SO → DO queda bloqueada cq comunicación que atraviese el enlace rojo. Es decir, cq comunicación que conecte las fuentes:

S8, S16, ..., S56

con los destinos:

D1, D1, ..., D7